这一周,台积电接连官宣了2个爆炸性的消息。

首先是台积电高级副总裁Y.P. Chin代表公司宣布:台积电即将开设2nm芯片研发中心。

紧接着,台积电(南京)有限公司总经理罗镇球确认,3nm芯片将在2022年进入量产阶段。

3nm芯片还没开始量产,台积电的2nm芯片研发就进入了公众的视线。

8月25日,多头成功为台积电守住了当日的股价,股价收盘录得1.44%的小幅上涨,换手率录得1.04%;26日,台积电涨幅进一步扩大至2.14%。

按照以往的规律,随着芯片纳米数量级越来越小,芯片制造将会越来越接近摩尔定律的天花板。

这意味着芯片的升级换代将带来更大的成本,而提高芯片密度带来的性能提升,也将进入一个明显的边际效益递减的过程。

但在芯片制造领域已经取得领导地位的台积电,依旧选择一掷千金,快速将2nm芯片制程的研发提上日程。

更先进的技术

台积电这个名字,中国大陆的读者已经非常熟悉。

这家位于台湾地区的半导体制造商,在过去的2年里由于某些众所周知的原因,与中国高科技产业的命运联系在了一起。

与其说是联系,倒不如说是一种近乎单向的影响力。

台积电此前表示2020年9月14日之后不再向华为高端芯片代工服务,由此带来的后果大家都知道了——由于没有其他代工厂可以进行生产,华为基于7nm制程生产的麒麟系列高端芯片成了“绝唱”。

台积电官宣的这座2nm工艺研发中心将会拥有一条先进的生产线,同时配套以8000名工程师。

研发中心可能位于台湾地区的南部科学园。此前就有报道称台积电正在园区内斥资1.25亿美元建造一座工厂。不过当时台积电没有透露工厂的用途。

从技术上看,台积电这次开始研发的2nm芯片工艺将会导入GAA-FET晶体管结构。

截止目前,台积电的3nm芯片依然在使用Fin-FET工艺。尽管台积电的3nm芯片已经完成了研发,但距离量产还有一段距离,更不用提已经带来的收益。

在这样的情况下,台积电对2nm制造工艺的布局,显得步子会不会有些大?

GAA-FET,台积电在琢磨啥?

台积电会因为步子大而扯着跨吗?这次投资和收益是否会成正比?

这要看台积电希望达到什么目的。

而要了解台积电此次布局2nm芯片的动机,我们必须先简单了解一下这次2nm芯片采用的GAA-FET工艺本身。

故事得从GAA-FET的“前辈”Fin-FET说起。

FinFET工艺全称Fin Field-Effect Transistor,中文名叫鳍式场效应晶体管。这样的命名,来源于晶体管的形状与鱼鳍的相似性。

在一些晶体管密度较大的芯片中,这种设计可以大幅改善电路控制并减少漏电流(leakage),也可以大幅缩短晶体管的栅长。

曾几何时,传统技术在遭遇瓶颈的情况下,Fin-FET成功为“摩尔定律”续了命,推动芯片朝着20nm及以下更高晶体管密度的方向继续发展到7nm,5nm甚至是3nm。

然而Fin-FET芯片的尺寸进一步缩小至3.5nm后,无论是鳍片距离、短沟道效应、还是漏电和材料极限,都使得晶体管制造都逐渐接近天花板了。

于是比FinEFT提出要早上10年的GAA-FET又重新被写进了台积电的日程表。

GAA-FET全称Gate-All-Around-Effect Transistor,即切入环绕式栅极技术。

顾名思义,这种技术与Fin-FET相似,但要求晶体管内部的硅通道完全被栅极材料包围,而不是像Fin-FET一样被栅极材料覆盖。

因此,这种技术可以增加晶体管密度,同时增加沟道的缩放潜力,解决了电压调节的问题进而降低电压缩放造成的功耗,同时还能提高性能。

业界认为,GAA-FET为半导体代工业务提供了一种超越FinFET设计的方法。

尽管这些改进的具体时间表可能不会像行业过去那么快,但至少关于它们是否会到来的不确定性现在可能会逐渐改观。

对于芯片和器件制造商而言,这些技术进步为半导体制造业的未来提供了更清晰的视角,并且应该让他们有信心推进积极的长期产品计划。

投入很大,产出很小?

但不容忽视的是,随着芯片的密度的日益提升,芯片更新换代能够带来的收益,反而逐渐进入了一个边际效应递减的过程。

就连摩尔定律的发现者,英特尔公司联合创始人戈登·摩尔都认为,“摩尔定律”必将终结。

我们在现有的芯片上,已经看到更新换代所带来的性能提升,有些增长乏力。

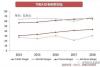

台积电曾经对自己的7nm工艺跟10nm工艺进行对比,结果是性能提升了20%、功耗降低40%、芯片密度是10nm的1.6倍。

然而到了5nm工艺的时候,芯片的性能比7nm提高了15%、能耗降低20%、晶体管密度提高1.8倍。

而与5nm工艺相比,3nm芯片的性能提升5%,能耗降低15%,晶体管的密度提高1.7倍。

然而芯片越是高端,其研发成本就越是高的吓人。

研发16nm芯片的制造工艺,大约需要16.43美元的研发成本,10nm为16.37美元,7nm成本18.26美元,5nm和3nm分别涨到23.57美元、30.45美元。

芯片本身的开发,也遵循同样的规律。

10nm芯片的开发成本已超1.7亿美元,7nm接近3亿美元,5nm超5亿美元,基于3nm开发的复杂芯片,设计成本更将高达15亿美元。

一句话总结:投入越来越高,性能的提升却越来越小。

不过面对高企的研发成本,台积电似乎并没有放慢脚步。

除了在南部科技园的厂房和8000名工程师之外,台积电最近还被外媒爆料,为配合2nm工艺的研发计划而一口气购买了2台光刻机。

2020Q2台积电的期末现金流余额录得4676.13亿新台币,同比减少了28.03%;

2020H1固定资产交易带来了3190.76亿新台币的现金流出,较上年同期扩大了48.87%;

2020H1台积电的研发费用录得498.62亿新台币,同比增长19.26%,占营收比重达到8%

据外媒的初步预计,台积电2020年的资本支出将进一步提升,达到160亿美元左右。

台积电是“疯”了吗?

赛道上的进攻与反攻

如果非要说台积电布局2nm的举动十分“疯狂”,那也是被竞争对手逼“疯”的。

纵观全球半导体市场,目前只有台积电和三星两家能够踏足3nm领域的芯片制造,两家之间的技术差距相对比较近。

然而三星对GAA-FET工艺的布局比台积电要早得多。

2019年5月14日在美国加利福尼亚州圣克拉拉举行的2019年三星代工论坛上,三星宣布将于2020年完成GAA工艺开发,并于2021年开始量产导入GAA工艺的3nm芯片。

值得注意的是,当时三星的芯片制造工艺由由5nm直接上升到3nm。4nm则被直接跳过了,其目的是为了抢在台积电之前完成3nm的研发。可见三星与台积电在3nm领域一较高下的决心。

2020年年初,三星成功试产了3nm芯片。

但三星的3nm之路在随后被突然打断,其激进的量产计划却因为新冠疫情爆发,被迫推迟到2022年。

这与台积电宣布要量产3nm芯片的时间节点,又来到了同一起跑线上。

反观台积电芯片研发的路径,则一直是稳扎稳打——从7nm到5nm,再到4nm和3nm,一步一个脚印。

不过在基于Fin-FET工艺的3nm制程刚完成研发、相关芯片尚未开始量产的时候,台积电便迅速调转马头,斥巨资投入GAA赛道,可见台积电也开始加快脚步了。

对于台积电来说,这次布局2nm的芯片制造,需要完成从Fin向GAA的转型。

对于三星来说,由于已经研发完成了GAA的研发,下一步需要利用这项技术来生产更高密度的芯片。

同一起跑线上的两种路径,谁比较快、谁走得更远,只有交给时间来验证。

慢人一步的慢性死亡

一边是台积电和三星之间打得飞沙走石,另一边则是“佛系”芯片公司,他们在纳米数量级和制造工艺的研发上,步子走得很慢。

这些公司包括曾经的“一骑绝尘”的芯片巨头英特尔。

从2014年推出14nm芯片开始,英特尔在14nm工艺优化的道路上可谓是越走越长。

2016年,在10nm的“战争”又爆发的时候,英特尔另辟蹊径,提出了“工艺、架构、优化”(P.A.O.)的策略模式,推出了14nm+,随后又在此基础上又推出了14nm++。

于是又人调侃英特尔的这种“挤牙膏”行为,称英特尔的终极目标是研发出14nm++++++。

其实英特尔并不是只有14nm的芯片,只是由于良品率问题导致其10nm芯片一再跳票。在2020年8月,英特尔的经济工程师们终于揭开Tiger Lake 10nm CPU微架构面纱,后者将出现在9月2日发布的产品中。

然而其他厂商的7nm芯片早已经走向商用。

曾经的英特尔在半导体领域是“一骑绝尘”的存在,如今已经无法与台积电和三星展开正面较量。

不过高密度芯片研发的进展缓慢,对于英特尔来说也只不过是温水煮青蛙式的慢性“死亡”

对于中国芯片制造商来说,形势则更加严峻。

7nm制程的芯片已经是中国大陆的芯片代工厂无法企及的高度。

然而到目前为止,被寄予厚望的中芯国际等中国制造商,能够做到的仅仅是在14nm制程芯片的基础上进行优化,使其性能达到与7nm芯片相近的水平。

华为麒麟系列高端芯片成了“绝唱”就是直接的后果。这也难怪华为已经开始自己研发芯片制造的技术。

只是当华为研发成功的时候,台积电的芯片制程又会缩小几个数量级呢?

小结

芯片行业的门槛有多高,自然已不必赘述。因此成功掌握了核心科技的上游玩家们,在整个游戏中将会赢家通吃。

这也是为什么台积电和三星两家竭尽所能力争“上游”。

而对于下游和低端玩家,另辟蹊径也许能够获得弯道超车的机会,但无法取得突破的话终究是一场温水煮青蛙的慢性“死亡”。

这两年中国半导体行业在“制裁”中学到的教训是:在落后的情况下,还需要加大投入、提前布局,方能在不进则退的赛道上立于不败之地。