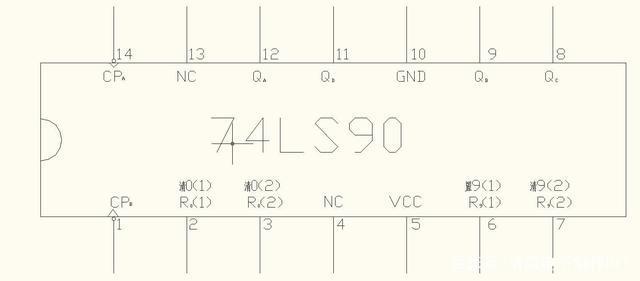

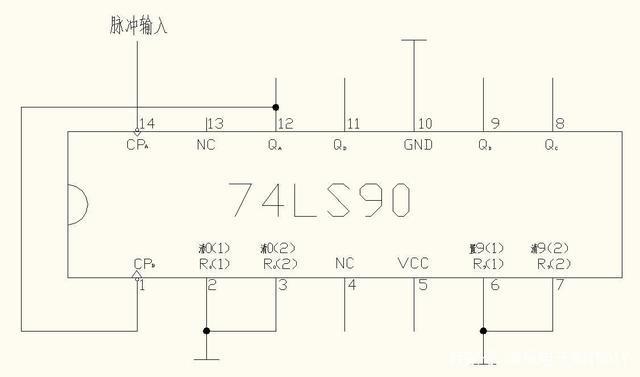

74LS90是一种中规模的二五叶进制计数器,其各引脚功能如图所示,

芯片引脚图

芯片引脚图

其中CPa和Qa构成1位二进制计数器,CPb和Qd、Qc、Qb 组成五进制计数器,将两个计数器有关端子适当组合,可以组成其他类型的计数器。

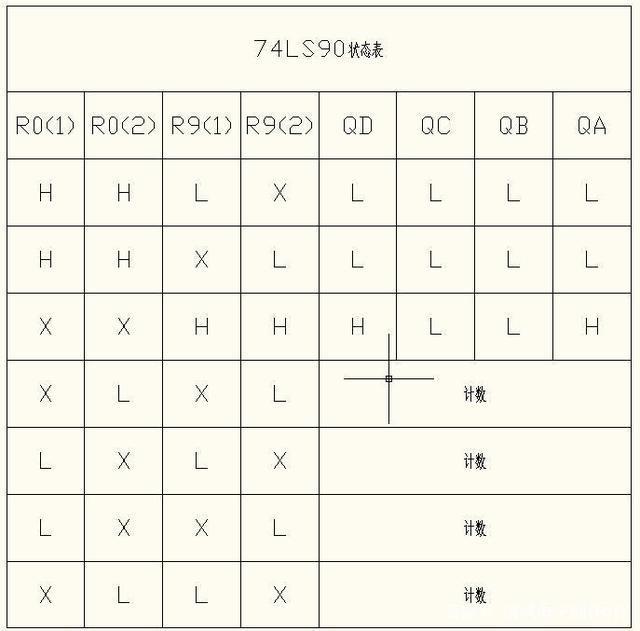

R0(1)、R0(2)为两个清0端,R9(1)、 R9(2)为两 个置9端,这4个端子与74LS90的工作状态关系 见表。

74LS90状态表

74LS90状态表

从表中可以看出:当R0(1)、R0(2)均为高电平且R9(1)、 R9(2)中有一个低电平时,计数器 QdQa端均被清0;当R9(1)、 R9(2)均为高电平时,Qd、Qa端均为高电平;当R0(1)、 R0(2)中有一个为低电平且时R9(1)、 R9(2)中也有一个为低电 平时,计数器工作在计数状态。

漂亮的电路板

漂亮的电路板

(1) 1位二进制计数器

74LS90的CPa和Qa构成1位二进制计数器,当CPa端输入第1个时钟脉冲时,Qa=1, 输入第2个脉冲时,Qa=0.

(2) 五进制计数器

CPb和Qd、Qc、Qb组成五进制计数器,当CPb端输入第1个脉冲时,QdQcQb=001,输 入第2个脉冲时,QdQcQb=010.输入第3、4个脉冲时,QdQcQb变化为011、100,输入第 5个脉冲时,QdQcQb变为000。

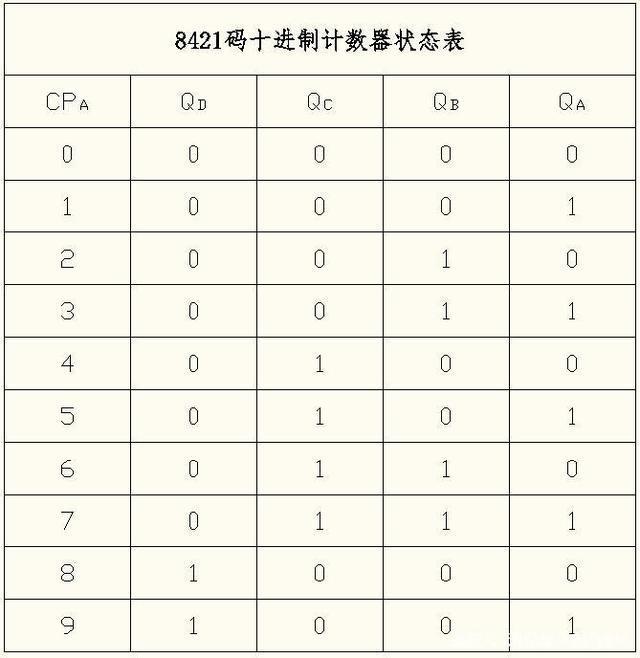

(3) 8421码十进制计数器

将1位进制计数器的输出端Qa与五进制计数器的CPb连接时,可组成8421码十进制计 数器,如图所示。

8421接线图

当09个时钟脉冲不断从CPa端输入时,QdQcQbQa状态变化为 0000、0001、0010-1000变化到1001,第10个时钟脉冲输入时,QdQcQbQa变为0000,具 体见表

8421码计数器状态表

8421码计数器状态表