Assoc教授Massimo Alioto(中)和他的团队成员Lin Longyang(左)和Saurabh Jain(右)展示了用于测试硅芯片的原型板,展示了高度灵活的功率和性能,超过了行业标准的电压等级。

来自新加坡国立大学的一组研究人员发明了一种新型的重构技术,它能自适应地扩展数字电路的最低功耗和最高性能,远远超过普通的电压调整。这种扩展适应允许数字硅芯片在正常使用期间以更低的功率运行,并在必要时以更高的性能水平运行。

在由收割机(例如太阳能电池)或充电电池供电的系统中,这可以在不确定电力可用性的情况下延长电池寿命,同时提供更高的峰值性能,以便在发生感兴趣的事件时进行片上数据分析。这是物联网(IoT)、人工智能(AI)、可穿戴设备和生物医学设备等应用的关键推动者。

“我们的重新配置技术引入了前所未有的适应性,以波动的电力可用性和性能需求。与行业标准的电压缩放技术相比,在我们实验室的几个测试芯片上的测量表明,这种适应性将移动或可穿戴设备的电池寿命延长了1.5倍,峰值性能也提高了一倍。我们的技术也可以用于进一步小型化电池的相同因素,同时保持相同的电池寿命,”副教授Massimo Alioto解释说。他是这一技术突破背后的新加坡国立大学绿色集成电路小组的领导。

他补充说,“进一步的好处是,我们的电路技术的功率性能通用性允许半导体公司简化他们的芯片组合,降低设计成本,因为相同的数字设计可以在广泛的应用和市场中重复使用。”

提出的技术已经导致演示加速器和处理器(例如,快速傅里叶变换,ARM处理器)与最小的能源消耗报告到目前为止。这项新技术的研究得到了领先的半导体公司(英特尔、台积电)、新加坡教育部和新加坡国家研究基金会的支持。

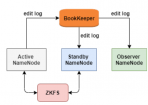

数据和时钟路径适应:实现低最低功耗和更高的峰值性能

大多数先进的移动、物联网和人工智能应用程序都需要在平均功耗(即平均功耗)之间进行灵活而广泛的权衡。以及决定系统响应性的最大性能(例如,当屏幕被触摸时,或者当传感器产生感兴趣的数据时进行数据分析)。

目前,动态电压调整是实现这种灵活性的黄金标准。在1v左右的电压下工作可以获得最大的性能和能耗,而在0.4-0.5 V电压下工作可以降低4- 5倍的能耗,并使工作速度降低近10倍。这种方法的缺点是电压缩放一般适用于固定的数字架构,尽管在能耗和性能方面的最佳架构取决于所采用的电压。

由NUS团队演示的自适应数字电路能够通过降低正常使用下的功耗来延长智能硅芯片的电池寿命,同时扩大性能以快速响应偶尔的数据事件。

NUS的发明优于电压缩放,因为它的电路重构使架构与所采用的电压更好地匹配,从而可以在不同电压下进一步降低能耗和提高性能。

Alioto副教授说:“我们的发明可以重新配置实际处理的“数据路径”和分配时钟信号来协调不同处理任务的“时钟路径”。在这两种情况下,它们的基本构建块被灵活地合并或拆分,以创建数据和时钟路径结构,在给定的电压下提高能效或性能。”

与传统的电压调整相比,由新加坡国立大学绿色IC集团提出的方法使数字电路更加灵活和自适应,允许在功率性能谱的两端同时优化。

技术书籍和一个完整的工具链公开提供

为了与全世界的工业和研究团体分享该团队的新技术的好处,最近出版了一本技术书籍,提供了处理器、加速器和芯片内存储器的硅芯片实现的背景和细节。自动化设计流程也已经创建并在GitHub上公开发布(请访问http://www.green-ic.org/)。

在我们的书中,我们介绍和演示了使用单独的商业设计工具的设计方法,这些工具被集成到一个内聚设计流程中,其中时钟和数据路径重构以即插即用的方式被合并。我们很高兴能以开放源码的方式分享软件代码,使我们的新技术在商业领域和学术研究中得到大规模和快速的应用。”

下一个步骤

新加坡国立大学的研究团队目前正在研究开发新型智能硅系统,该系统允许在嵌入到传感硅片的人工智能加速器中实现超宽的功率性能适应。这将导致下一代系统始终可用,同时能够迅速响应外部事件,具有非常显著的计算性能。

在他们的工作中,团队努力通过drop-in技术和现有系统架构中的设计方法来实现动力性能适应。这使得在不破坏设计生态系统的情况下实现动力性能优势,从而实现了下一代智能系统的快速和大规模采用。